Det gick så fort för styrkretstillverkarna att rita in den öppna cpu:n RISC-V i sina roadmaps att inte ens IAR hängde med i svängarna. Nu berättar företaget vad dess kunder och partners snickrar på i kiselverkstäderna.

Det gick så fort för styrkretstillverkarna att rita in den öppna cpu:n RISC-V i sina roadmaps att inte ens IAR hängde med i svängarna. Nu berättar företaget vad dess kunder och partners snickrar på i kiselverkstäderna.

Från början var RISC-V en cpu för undervisning, och den tycks konstruerad när-mast med server och pc för ögonen. Men det står nu klart att det blir som mikrokontroller eller styrkärna som RISC-V får sitt första genombrott.

|

|

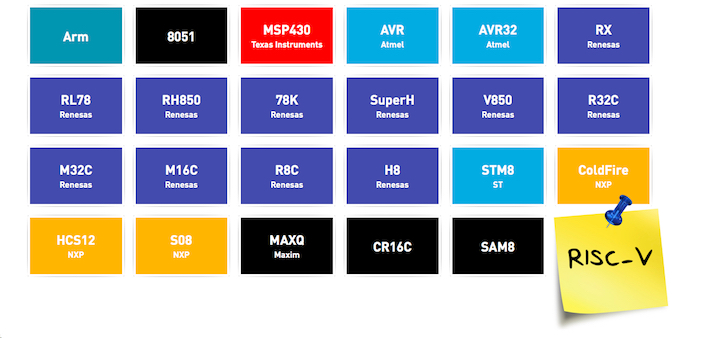

År 2019 ska RISC-V bli IAR:s 24:e arkitektur, med samma utbud av verktyg, kompilatorer, debuggers och prober som de övriga. |

När svenska IAR i februari meddelade att företaget arbetade på en kompilator för RISC-V, raderade Elektroniktidningen sitt sista frågetecken inför den nya omsusade gratisarkitekturen.

IAR är det perfekta vittnet. Företaget tjänar för det första sitt levebröd på effektiva kompilatorer. För att kunna krama den sista droppen prestanda ur de genererade maskininstruktionerna måste du behärska ämnet processorarkitektur ner till minst signifikanta carry-bit.

IAR i Uppsala har varit världsmästare i kompilatorer för styrkretsar under många år nu. Det är hit tillverkarna går när de ska benchmarka sina nya kretsar för att få snabb, snål, minimal och korrekt kod.

Elektroniktidningen smickrar och företagets chefsstrateg Anders Holmberg instämmer belåtet.

|

| Anders Holmberg |

– Vi har ett gediget kvalitetsrykte.

För det andra är IAR en neutral part i styrkretsvärlden, med sitt stöd för alla de viktiga arkitekturerna mellan åtta och 32 bitar.

För det tredje har IAR ett djupt kontaktnät och vet hur vindarna blåser, vad som finns och vad som planeras av vem och när.

Det var via sitt kontaktnät IAR först började inse att RISC-V måste tas på allvar.

– Vi hade varit lite tveksamma att ge oss in i det nya ekosystemet. Om du backar säg ett och ett halvt till två år, så såg vi inget business case.

Men plötsligt började IAR få förfrågningar från existerande kunder. Och från hårdvarupartners. Och från helt nya spelare. De förväntade sig att IAR självklart skulle släppa sina verktyg även för RISC-V.

– Bilden förstärktes ju mer vi rotade. Så till den milda grad att man i efterhand kanske kan tycka att vi borde varit snabbare på tåget.

Han beskriver RISC- V som ett välkommet syretillskott till inbyggnadsvärlden.

– Det händer någonting nytt efter att Arm helt dominerat i tolv, tretton år.

Genomslaget blev fullt synligt på en utvecklarkonferens i fjol.

–RISC-V är ju egentligen en gammal arkitektur som bubblat under många år. Men åh jäklar, plötsligt var alla där! Alla våra traditionella partners plus de nya spelarna dök upp. Innan dess hade man möjligen kunnat avfärda RISC-V som en nischföreteelse.

Western Digital utvecklar två RISC-V-kärnor för sina egna minnesprodukter och Nvidia integrerar RISC-V någonstans i sin portfölj. Det är de idag offentligt kända exemplen på stora användare.

Det gemensamma är att de använder RISC-V som styrkärna i egna systemkretsar.

– Vi vet att det finns ett antal som är på gång. Det är en tydlig trend: bolag som bygger specialiserat kisel för specifika tillämpningar och som överväger att ta sin nästa produkt till RISC-V.

Som marknaden ser ut är det huvudsakligen Arms olika Cortex M-kärnor som RISC-V tacklar undan.

ARM vs RISC-V |

|

RISC-V liksom ARM är en instruktionsuppsättning eller en ISA (instruction set architecture) vilket är en samling instruktioner som fungerar som det språk en programmerare använder för att styra en processor. Eller i praktiken snarare som en kompilator använder. Programmeraren skriver sitt program i ett mer lättbegripligt så kallat högnivåspråk. Därefter översätter en kompilator – från till exempel IAR – programmet till RISC-V-instruktioner. RISC-V är avsiktligt konstruerad i ett försök att kunna omfatta hela spannet av cpu:er från 32 bitar och upp. Det finns inte bara en RISC-V-ISA utan många varianter, som i ARM-familjen. Sammantaget blir det ett stort antal om man räknar samman alla teoretiskt möjliga varianter. De namnges efter en kombination av ordlängd och fjorton tillägg, som flyttalstöd, vektoroperationer, bitmanipulering, med mera. I RISC-V-världen är ISA:t gratis och dessutom fritt att modifiera. Det är den mest grundläggande skillnaden. Det finns gratiskärnor att ladda hem, men även en marknadsplats för licenserbara kärnor, liksom det gör för ARM. Två namnkunniga bolag inom RISC-V idag är amerikanska Sifive och taiwanesiska Andes. På Sifive hittar du flera av RISC-V:s grundare. Intel finns bland investerarna. Andes är den i RISC-V-stiftelsen som är mest drivande inom inbyggda system. – Det var mycket på deras initiativ som vi gick med i RISC-V-stiftelsen, berättar Anders Holmberg. Företaget är en gammal cpu-licenserare som tidigare haft sitt fokus på Taiwan och Kina och använt sin egen arkitektur. Idag styr Andes över till RISC-V och saluför hittills fyra olika RISC-V-familjer. |

– Pratar man med Arm är de bekymrade. Det är helt klart. De ser en utmaning. De får konkurrenter med helt andra affärsmodeller som säljer något som är funktionellt ganska likt det de själva säljer, men till en prislapp som kan vara dramatiskt lägre över tid.

Cortex M släpptes 2005. Den adopterades snabbt av bland annat ST och NXP vilket blev startskottet för Arms nuvarande styrkretsdominans. Konkurrenter som Arc och Mips har därefter endast lyckats kapa åt sig mindre nischer.

–Jag tror att deras erbjudanden har varit för lika. Det har inte funnits någon dynamik.

Arms PR-avdelning gjorde i somras ett misslyckat försök till motstöt mot RISC-V, genom att sätta upp en sajt med egna fakta på domänen riscv-basics.com.

Det uppfattades som billig smutskastning och slog rejält fel. Arms egna ingenjörer tvingade PR-avdelningen att stänga sajten efter några dagar.

De första generella styrkretsar där RISC-V inte bara är en extrakärna i en systemkrets utan hjärtat i sin egen programmerbara krets, kan komma att bli kinesiska.

– I Kina är man ju generellt inte så sugen på att betala. Och så vill de bygga upp en egen datorindustri – där kan RISC-V bli en komponent.

Detsamma gäller Indien som omfamnat RISC-V för de möjligheter den ger till ”oberoende och innovation”. Landet har till och med utnämnt det till sitt nationella ISA.

Vad säger NXP, ST och andra traditionella MCU-tillverkare?

– Jag kan inte gå in så mycket på det. Vi har tajta relationer så det är känsligt. Men det står klart att de är väl medvetna om vad som sker och att de funderar på vad de ska göra med RISC-V.

– För dem är det också en politisk utmaning. De har långvariga relationer med Arm och mycket kan stå på spel om man plötsligt vill välja en annan väg.

Hur stor tror du RISC-V kan bli till slut?

– Det är en knepig fråga att svara på. Men vi tror att det kommer att bli en signifikant del av våra affärer så småningom.

– Inte om ett eller två år, men på fem, sex, sju års sikt tror vi att det kommer att ta en ganska stor del av marknaden, åtminstone för microcontrollers.

Kommer RISC-V att tränga sig in även på Cortex-A:s område?

–Jag tror det. Vi är inte jättestarka på Cortex-A, men vi vet ju till exempel att både Sifive, Andes och andra aktörer redan idag bygger Cortex A-klass-processorer tänkta för high end-operativsystem, typiskt Linux.

– Och de lägger ganska mycket krut på det, för det finns mycket pengar att hämta där, framför allt på servermarknaden.

Friheten är både möjlghet och risk |

|

Gratis är gott, men det viktigaste med RISC-V är liksom i Linuxvärlden de möjligheter som öppnas för innovation när arkitekturen är öppen. De instruktionsuppsättningar som används i Armprocessorer är bundna av intellektuella rättigheter. Du får inte bygga en processor som använder ARMv8 utan att betala licens och royalties till ägaren Arm Holdings. – Som RISC-Vspelare kan du välja alternativ som är helt gratis. Eller gå till någon med en färdig design, men med en prislapp som oftast ser helt annorlunda ut. En kanske ännu större fördel för RISC-V är att det står vem som helst fritt att göra anpassningar för den egna tillämpningen. Hos Arm är du låst. – Visst är det kul att betala mindre för i princip samma funktion i RISC-V. Men innovation är det som folk pratar om, att du kan anpassa designen och göra vad du vill. Du har i normalfallet inte rätt att skruva på en Arm så att den bli aningen mer strömsnål eller snabb. Eller ta bort instruktioner du inte behöver. Du kan köpa rätte för pengar som endast en handfull företag kan lägga upp, som Qualcomm, Apple och Samsung i mobilprocessorvärlden. Men även om du väljer att lägga in en extra instruktion i Arm, för exempelvis ett acceleratorblock för artificiella neuronnät, så har du fortfarande inte samma frihet som i RISC-V. Nu är vi inne på de riktigt fina detaljerna i skillnaderna. Arms komponenter är standardiserade. Det finns regler du måste följa och fasta byggstenar som du måste använda när du implementerar egna instruktioner. Arkitekturellt är det en ren och fin lösning med uppenbara fördelar, till exempel i att kärnor från olika håll kan pusslas samman enkelt och enhetligt. Men RISC-V:s friheter skapa fler möjligheter till optimering. Du kan skruva på gränssnitt, minnesbussar, pipelines och andra delar av konstruktionen. – Eftersom du kan göra fler specialanpassningar och inte behöver bygga så extremt generellt som när du använder byggstenar från Arm, finns det en potential i en RISC-V-design att både kunna minska kiselytan och öka prestandan. Baksidan av samma frihet drabbar IAR när företaget ska försöka sätta ihop en kompilator till din specialbyggda ISA. Så länge som RISC-V-processorer nöjer sig med grundinstruktionerna kan de köra samma program. Men med egna instruktioner försvinner kompatibiliteten. Det är ett problem som IAR nu grubblar över. – Hur ska vi hantera egna instruktioner för att ge bäst prestanda för en nisch? En handfull egna instruktioner kan gå bra. Men det finns en gräns. IAR måste tänka nytt. – Hur stöder vi diversifieringen? Kan man till exempel ge användaren möjlighet att skräddarsy verktygen för sina egna tillägg? Här har vi inte riktigt tänkt klart. Det är för tidigt att se ännu vad folk kommer att hitta på. Att hålla denna frihet i schack kan till och med vara en nyckelfråga för ARM:s överlevnad. –Allt kan falla ihop som ett korthus om RISC-V blir för spretigt. |