Amerikanska Rambus avslöjar hur företaget med olika metoder ska stödja datatrafik upp mot 3,2 Gbit per sekund mellan DRAM och processor utan att strömförbrukningen ökar nämnvärt med idag. Det utstakade målet är att klara de krav som kommer att ställas år 2011 och därefter – bortom DDR3.

Nu hoppas företaget att industrin antar tekniken som en del i en framtida DRAM-standard. Konceptet är intressant. Ändå måste man fråga sig hur intresserade de stora DRAM-tillverkarna är av att samarbeta med Rambus efter år av patentstrider, som ännu inte är avgjorda (se länk). Trots alla konflikter jobbar Rambus vidare med att förbättra datatrafiken mellan minne och processor i morgondagens system. När nästa minnesgeneration, DDR4, blir verklighet måste datatrafiken per anslutning dubblas till 3,2 Gbit/s, hävdar företager. Likaså måste effektförbrukningen reduceras rejält, speciellt i viloläge.

– I många system är minnet i vila över 90 procent av tiden, förklarar Michael Ching, ansvarig för strategisk utveckling på Rambus.

För att nå målen föreslår Rambus ett minnesgränssnitt som lutar sig mot två nya innovationer kombinerade med tre äldre. De nya är en färsk variant av Near Ground Signaling samt så kallad Module Threading.

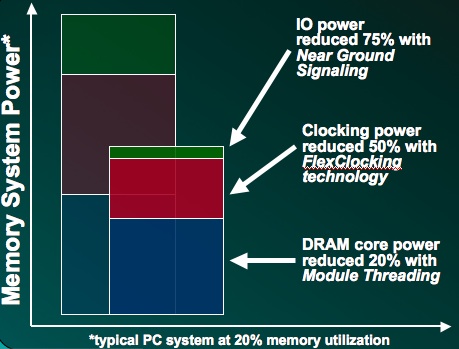

Near Ground Signaling introducerade Rambus egentligen redan i februari på mässan Mobile World Congress i Barcelona, men då med differentiell teknik. Nu talar man om en entrådsteknik som ska klara signalsving på bara 0,5 V utan problem med signalintegriteten. Rambus hävdar att tekniken kan minska in- och utgångarnas effektförbrukning med 75 procent jämfört med idag – självklart förutsatt att datatakten är densamma.

– Med differentiell teknik skulle vi kunna nå än lägre effektförbrukning, men singel-ended-tekniken ger flera fördelar. Framförallt får man färre anslutningar och enklare routing, säger Michael Ching.

Med Module Threading delar företaget upp minnesmodulen i två parallella trådar. De två trådarna genereras genom att en modul accessas från var sin ände så att fyra istället för åtta minnen läses i taget. Tekniken ökar minnets genomströmning med upp till 50 procent samtidigt som DRAM-kärnans effektförbrukning minskar med 20 procent, enligt Rambus.

– Dessa två innovationer kombinerade med vår Flexclocking-teknik kan minska den totala effektförbrukningen i minnessystemet med 40 procent, säger Michael Ching.

Flexclocking är en klockarkitektur som gör det möjligt att förenkla gränssnittet på minnessidan samtidigt som effektförbrukningen i vila minskas markant. Rambus introducerade tekniken på Mobile World Congress inom initiativet Mobile Memory med fokus på framtida mobiltelefoner.

Till de nämnda teknikerna vill Rambus även addera de två teknikerna Flexphase och Dynamic Point-to-Point (DPP), som sedan tidigare används i företagets minnesarkitekturer XDR. Flexphase stöder högre datahastigheter än den teknik som användas i dagens DDR3-minnen, medan DPP är en signaleringsteknik ämnad att ökar kapaciteten två till fyra gånger mellan minne och processor.

– Genom att kombinera de fem nämnda teknikerna kan vi öka bandbredden med det dubbla jämfört med dagens DDR3 och samtidigt se till att effektförbrukningen håller sig inom rimliga gränser, säger Michael Ching.

Företaget har släppt ett vitpapper som förklarar detaljerna kring tekniken.